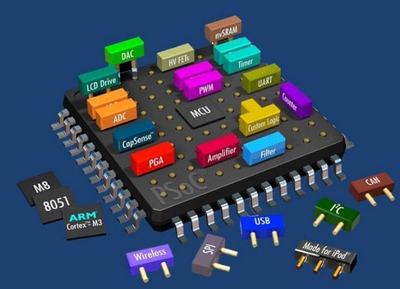

《CMOS集成电路后端设计与实战》是学习集成电路物理设计的经典教材,其配套的Lab实验是掌握后端流程(从Netlist到GDSII)的关键实践环节。独立完成这些实验不仅能巩固理论知识,更能培养实际工程能力。以下是一份详尽的、手把手的自学指南,旨在帮助你脱离依赖,独立攻克这些实验。

第一步:实验环境搭建与工具准备

- 获取实验资料:确保你拥有完整的实验数据包,通常包含标准单元库(时序、功耗、物理库)、设计网表(Netlist)、约束文件(SDC)、技术文件(Tech File)及脚本模板。

- 安装EDA工具:实验通常基于Synopsys或Cadence等商业工具链(如Design Compiler, IC Compiler II/Innovus, StarRC, PrimeTime)。作为学习者,可以申请教育版License或使用功能受限的免费版本。务必仔细阅读工具的安装与配置文档,正确设置许可证和环境变量(如

LM<em>LICENSE</em>FILE,PATH)。 - 验证环境:运行一个简单的工具命令(如

icc2_shell -version或innovus -version)来确认工具可正常启动。尝试用附带的库文件做一个简单的读入操作,确保数据格式无误。

第二步:理论回顾与实验目标精读

不要急于操作! 在打开工具之前:

- 精读教材相关章节:明确当前实验在完整后端流程(综合、布局、时钟树综合、布线、签核)中的位置。理解每个步骤的目的、输入和输出。

- 逐字研读实验指导书:

- 明确最终目标:例如,“在满足时序约束的前提下,实现面积小于XX,功耗低于YY的物理版图”。

- 理解每一步指令:弄清每个命令或脚本参数的意义。如果不明白,立刻回顾教材或工具手册。

- 分析提供的脚本:实验通常会提供部分脚本。将其打开,加上自己的注释,理解每一行的作用。这是学习自动化流程的最佳方式。

第三步:分步执行与深度探索

遵循“运行-观察-分析-调整”的循环:

- 从第一步开始:例如,数据准备(读入库、网表、约束)。在工具命令行中手动键入关键命令,而非直接运行完整脚本。观察日志信息,确认数据成功载入。

- 记录与检查:每完成一个步骤(如初始布局),立即使用工具提供的检查命令(如

check_placement)并查看报告(面积、时序、拥塞报告)。将这些结果记录下来,与预期对比。 - 遇到报错怎么办?:

- 精准定位:仔细阅读错误(Error)和警告(Warning)信息,工具通常会给出出错的代码行或对象名。

- 独立排查:检查文件路径是否正确、文件格式是否匹配、变量是否定义、约束是否合理。这是培养debug能力的核心。

- 善用资源:将错误信息的关键词在工具官方文档、教材或Google(如“ICC2 ERROR ORD-...”)中搜索,绝大部分基础问题都有解答。

- 超越实验指导:在完成基本流程后,主动尝试:

- 调整参数:修改布局的密度目标、时钟树综合的缓冲区类型、布线的层数分配,观察其对时序、面积、功耗的影响。

- 分析折衷:尝试优化时序(可能增大面积和功耗),或优化面积(可能降低时序余量),理解后端设计中的权衡艺术。

- 可视化检查:熟练使用工具的图形界面(GUI)查看布局布线结果、时序关键路径、电源网络。直观理解比看报告更深刻。

第四步:结果分析与复盘

- 收集最终报告:时序报告(建立/保持时间违例)、面积报告、功耗报告、DRC/LVS验证结果(如果实验包含)。

- 进行结果分析:

- 你的设计是否满足了所有约束?如果没有,违例的主要原因是什麽?(是逻辑路径太长?拥塞导致布线延迟过大?)

- 对比不同优化策略下的结果,得出结论。

- 撰写实验笔记:用你自己的话,记录完整的操作流程、关键命令、遇到的错误及解决方法、最终结果和分析。这份笔记是你最宝贵的财富。

保持独立性的关键心态

- 把工具当作“黑盒”到“灰盒”:初期只需知道输入输出;后期应通过文档和实验,逐步了解其内部算法的基本原理。

- 问题分解:将一个大问题(如“有时序违例”)分解为小问题(是哪个寄存器?是哪条路径?是布局问题还是布线问题?)。

- 耐心与坚持:后端设计迭代周期长,一个实验可能需要数天甚至更久。每一次失败和排查都在增强你的实战能力。

通过以上系统性的方法,你将不再是被动地跟随步骤,而是能够主动掌控整个设计流程。你不仅能独立完成这本教材的Lab,更将获得应对真实集成电路后端设计挑战的坚实基础和自信。