模拟集成电路设计是现代电子系统的核心,它关乎信号的真实、精确与高效处理。在《模拟集成电路设计精粹》的第六章“集成电路设计”中,我们将深入探讨这一领域的核心概念、设计流程与关键技术,揭示从抽象概念到物理实现的完整路径。

一、集成电路设计概述

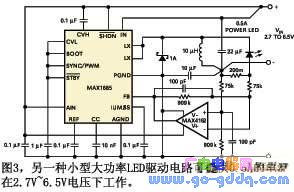

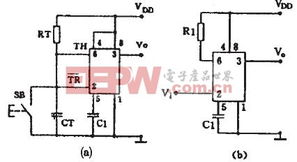

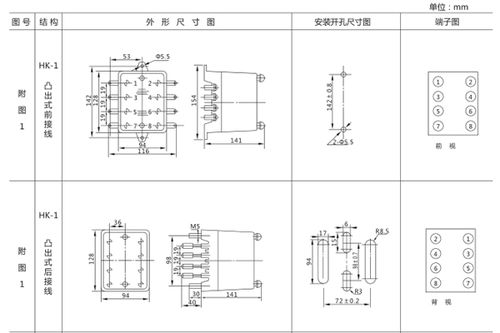

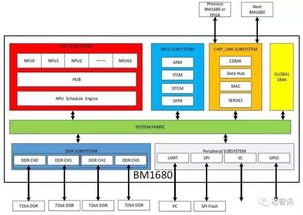

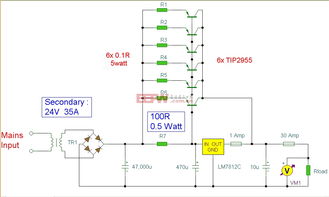

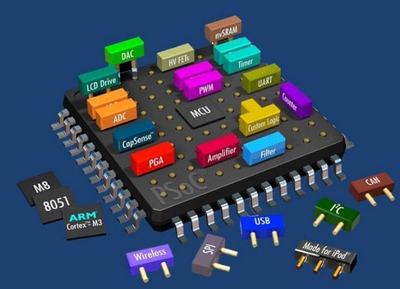

集成电路设计是将电路功能、性能指标转化为实际硅芯片版图的过程。模拟集成电路设计尤其注重性能的优化,如增益、带宽、噪声、功耗和线性度等。这一过程通常分为系统级设计、电路级设计、版图设计和验证等阶段。系统级设计确定整体架构和模块划分;电路级设计则聚焦于晶体管级电路实现,使用SPICE等工具进行仿真分析;版图设计是将电路图转换为物理布局,需考虑匹配、寄生效应和可靠性;验证则确保设计符合规格并具备可制造性。

二、关键设计原则与技术

在模拟集成电路设计中,几个关键原则至关重要。匹配性是模拟电路性能稳定的基础,例如在差分对或电流镜中,晶体管的尺寸、布局需高度对称以减少工艺偏差影响。噪声分析不可或缺,因为模拟信号易受热噪声、闪烁噪声干扰,设计时需优化器件尺寸和偏置以最小化噪声系数。电源抑制比和共模抑制比是衡量电路抗干扰能力的重要指标,通过采用共源共栅结构、带隙基准等技术可以显著提升。随着工艺节点缩小,短沟道效应、漏电流等问题日益突出,设计者需掌握深亚微米下的建模与补偿方法。

三、设计流程与工具链

现代集成电路设计依赖于成熟的工具链。设计流程通常以Top-Down方式展开:从行为级建模开始,使用Verilog-A或MATLAB进行系统仿真;进而进入电路级设计,采用Cadence Virtuoso等平台绘制原理图并进行DC、AC、瞬态仿真;版图阶段则使用物理设计工具,考虑DRC、LVS规则检查,确保制造可行性。寄生参数提取和后仿真验证是闭环的关键,以评估实际性能。本章还强调了设计复用和IP核的重要性,它们能加速开发周期,降低成本。

四、挑战与未来趋势

模拟集成电路设计面临诸多挑战,包括工艺变异性的管理、功耗与性能的权衡,以及混合信号集成中的串扰问题。随着物联网、人工智能和5G等应用的兴起,对高能效、高集成度模拟电路的需求日益增长。未来趋势指向更智能的设计自动化工具,利用机器学习优化电路参数;新材料如GaN、SiC的应用将拓展高频、高压场景下的设计边界。设计者需持续学习,融合跨学科知识,以应对不断演进的技术浪潮。

第六章“集成电路设计”不仅是技术的汇总,更是艺术与科学的结合。它要求设计者具备扎实的理论基础、丰富的实践经验和创新的思维模式。通过掌握这些精髓,我们方能打造出性能卓越、稳定可靠的模拟集成电路,推动电子技术向前发展。