集成电路设计是现代信息产业的基石,其最终物理实现依赖于精密的版图设计。本文将系统性地介绍从设计概念到物理版图的完整流程及其关键技术。

一、集成电路设计总览:分层实现之路

集成电路设计是一个典型的自顶向下(Top-Down)过程,通常分为以下几个层次:

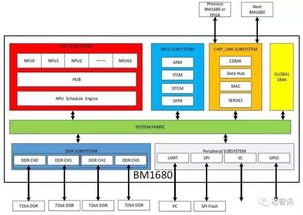

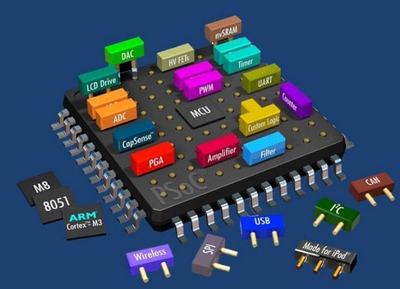

- 系统级设计:定义芯片的整体功能、性能指标和架构。

- 逻辑设计:使用硬件描述语言(如Verilog、VHDL)进行寄存器传输级(RTL)设计,实现功能描述。

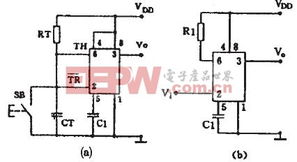

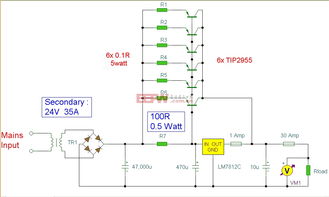

- 电路设计:将逻辑门转化为晶体管级电路,进行功耗、时序和噪声的初步分析。

- 物理设计(核心):即版图设计,将电路图转化为可供制造的几何图形(版图),是设计与制造的桥梁。

二、版图设计:物理设计的核心环节

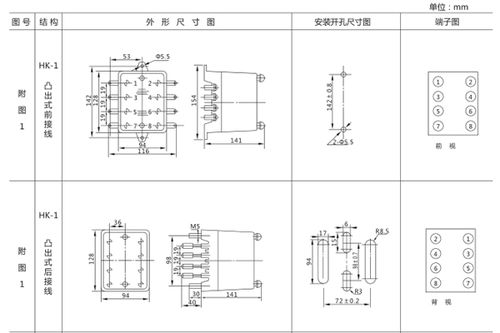

版图设计是集成电路设计的最后一步,也是决定芯片性能、面积、可靠性和制造成本的关键。其主要任务是根据电路原理图和工艺设计规则,绘制出每一层掩模的几何图形。

核心步骤包括:

- 布局:规划芯片上各个功能模块(如标准单元、存储器、模拟模块)的位置和形状,优化信号流与互连。目标是减小芯片面积、降低互连延迟和功耗。

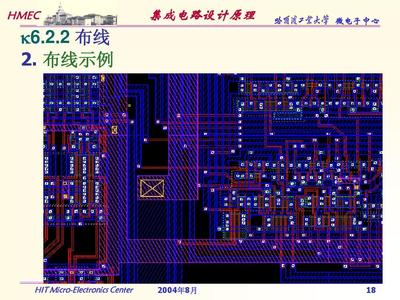

- 布线:在布局确定的模块之间,根据电气连接关系,在多个金属层上完成实际连线的绘制。必须严格遵守设计规则,并优化时序、信号完整性和功耗。

- 验证:确保版图完全正确,包括:

- 设计规则检查(DRC):验证版图是否符合制造工艺的物理限制(如线宽、间距)。

- 电路图版图一致性检查(LVS):确保绘制的版图与原始电路图在电气连接上完全一致。

- 电气规则检查(ERC):检查潜在的电气问题,如短路、开路、悬空节点等。

- 寄生参数提取与后仿真:提取版图中的寄生电阻、电容,进行更精确的时序和功耗分析。

三、关键技术挑战与设计方法

- 深亚微米/纳米级效应:随着工艺节点进入纳米尺度,互连延迟主导、功耗密度激增、制造变异增大等问题日益突出。版图设计必须考虑可制造性设计(DFM)、可靠性设计(DFR)和良率提升。

- 设计自动化(EDA)工具:现代复杂的版图设计高度依赖EDA工具链,包括自动布局布线(APR)、时钟树综合(CTS)、物理验证等工具,以应对数亿晶体管的设计规模。

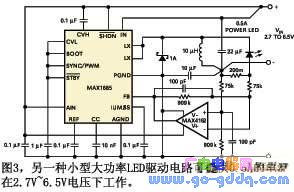

- 混合信号设计:对于包含模拟/射频电路和数字电路的芯片,版图需特别处理噪声隔离(如保护环、隔离阱)、匹配对称性及信号完整性等问题。

- 先进封装协同设计:在系统级封装(SiP)和芯片异构集成趋势下,版图设计需与封装规划、硅通孔(TSV)等三维集成技术协同考虑。

四、版图设计的价值与未来

版图设计绝非简单的“绘图”,而是融合了电路知识、工艺理解、物理效应建模和优化算法的复杂工程。一个优秀的版图设计师能在给定的约束下,实现性能、功耗、面积和成本的最佳平衡。随着人工智能与机器学习技术的发展,智能版图生成与优化正成为新的前沿,有望进一步提升设计效率与芯片质量。

从系统构想到最终掩模,集成电路版图设计是思想变为现实的最后一环,凝聚了无数工程师的智慧,持续推动着摩尔定律向前演进。