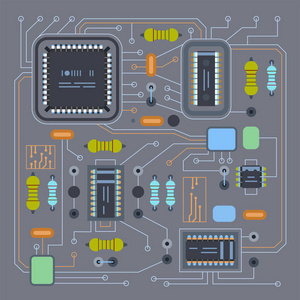

在当今数字时代的核心,隐藏着无数微小却功能强大的电子大脑——集成电路(IC),或称芯片。集成电路设计,正是赋予这些硅片以智能与生命的创造性过程。它是一门融合了电子工程、计算机科学和物理学的高度专业化领域,旨在将复杂的电路系统集成到一块微小的半导体材料上。

集成电路设计通常始于系统架构定义。设计师根据芯片的最终用途(如智能手机处理器、汽车传感器或人工智能加速器),确定其需要实现的功能、性能指标、功耗预算和成本目标。这一阶段如同绘制建筑的蓝图,需要宏观的视野与精准的规划。

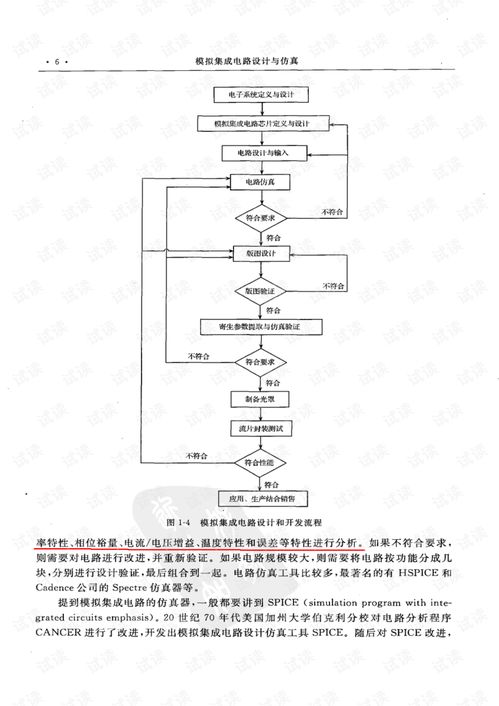

接下来进入关键的设计阶段,主要包括前端设计和后端设计两大流程。

前端设计(逻辑设计) 聚焦于芯片的功能实现。设计师使用硬件描述语言(如Verilog或VHDL),以代码形式描述电路的行为和结构。这个过程包括:

1. 设计输入:编写代码,定义逻辑门、寄存器、存储器等组件如何互联以实现特定功能。

2. 功能仿真与验证:通过软件模拟, exhaustive地测试设计在各种场景下的行为是否正确,确保逻辑功能符合预期。这是发现和纠正逻辑错误的关键步骤。

3. 逻辑综合:使用专用工具,将高级的硬件描述语言代码“翻译”和优化成由标准逻辑门单元(如与门、或门、非门)组成的网表,这个过程会考虑到目标工艺库和时序约束。

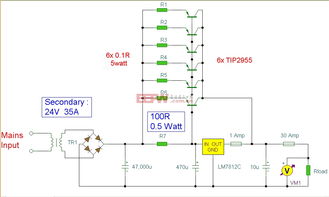

后端设计(物理设计) 则负责将逻辑网表转化为可供制造的物理版图。这是一个与硅片几何形状和制造工艺深度绑定的精密工程,主要包括:

1. 布图规划与布局:确定芯片上各个功能模块(如CPU核心、缓存、I/O接口)的大致位置和形状,以及电源网络的分布。

2. 时钟树综合:构建一个高效的时钟分布网络,确保时钟信号能够同步、低偏差地到达芯片的每一个时序单元,这是保证芯片高速稳定运行的基础。

3. 布线:根据布局结果,在多个金属层上实际连接所有逻辑单元和模块的引脚。布线必须遵守严格的制造设计规则,并优化信号完整性、时序和功耗。

4. 物理验证与签核:对生成的版图进行最终检查,包括设计规则检查(DRC)、版图与电路图一致性检查(LVS)、电学规则检查(ERC)以及精确的时序、功耗和信号完整性分析。只有通过所有验证,设计才能“签核”并交付给晶圆厂。

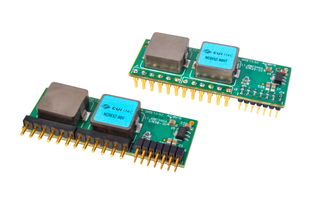

现代集成电路设计极度依赖电子设计自动化(EDA)工具。从仿真、综合到布局布线,EDA软件提供了强大的计算和自动化能力,使设计师能够管理数亿甚至上百亿个晶体管构成的超大规模设计。设计方法学也在不断演进,如基于IP核(预先设计好、经过验证的功能模块)的重用策略,极大地加速了设计进程。

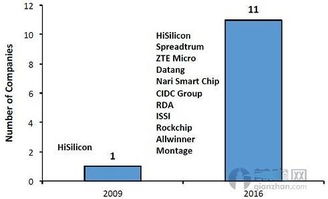

面临的挑战与日俱增。随着工艺节点向5纳米、3纳米甚至更小尺寸迈进,设计师不仅要追求更高的性能和更低的功耗,还必须应对量子隧穿效应、寄生效应加剧、制造变异增大等物理极限问题。日益增长的设计复杂度和研发成本,也使得协同设计、系统级优化和软硬件协同设计变得至关重要。

集成电路设计将继续向三维集成、异质集成(将不同工艺、材料的芯片封装在一起)、以及面向特定领域(如AI、量子计算)的定制化架构等方向探索。它不仅是信息产业的基石,更是推动人工智能、物联网、自动驾驶等前沿科技发展的核心引擎。从一颗沙粒般的硅片到驱动全球数字世界的强大引擎,集成电路设计无疑是人类智慧与工程技艺的巅峰体现之一。