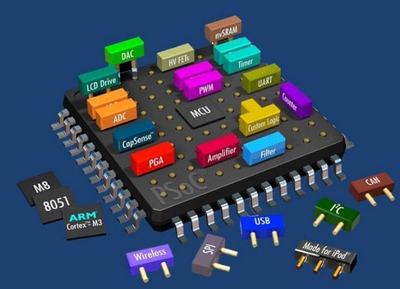

《Verilog HDL数字集成电路设计原理与应用》一书由蔡觉平教授编著,作为数字集成电路设计领域的经典教材,自出版以来深受广大高校师生及工程师的欢迎。本书系统阐述了基于硬件描述语言Verilog HDL的数字系统设计原理、方法与工程实践,是连接数字电路理论与现代芯片设计技术的关键桥梁。

在内容编排上,本书结构清晰,循序渐进。开篇首先回顾数字电路基础与集成电路设计流程,为后续学习奠定理论基础。核心章节深入讲解Verilog HDL的语法结构、建模方式(行为级、RTL级、门级)及可综合设计原则。作者不仅注重语法的详细解释,更强调如何编写高效、可综合的代码,避免初学者陷入仿真正确但无法实际实现的误区。书中通过大量实例,如计数器、状态机、存储器、简单处理器等,生动展示了从规格定义到代码实现、功能仿真、逻辑综合的完整设计流程。

本书的一大亮点在于其突出的应用导向。蔡觉平教授结合自身丰富的教学与工程经验,不仅讲解了语言本身,还深入探讨了同步设计方法、时钟域交叉、低功耗设计、可测试性设计等实际工程中的关键问题。附录中提供的EDA工具使用指南和实验指导,使得读者能够将理论知识迅速转化为动手能力,非常适合作为高等院校电子、微电子、计算机等相关专业的教材,同时也是一线工程师不可多得的参考手册。

在当当等图书平台的读者评价中,本书普遍被认可为内容详实、实例丰富、实用性强的优秀著作。读者反馈其讲解透彻,尤其适合Verilog HDL的入门与进阶学习。尽管数字设计技术不断发展,本书所涵盖的核心设计思想与方法论依然具有持久的价值。对于有志于进入芯片设计领域的学子,或是希望系统巩固数字设计知识的工程师而言,潜心研读《Verilog HDL数字集成电路设计原理与应用》无疑将获得扎实的技能储备与清晰的设计视野,从而在集成电路这一技术高地上行稳致远。