在上一部分介绍了集成电路(IC)的基本分类和设计流程概览后,我们进一步聚焦于超大规模集成电路(VLSI)设计的核心概念与环节。VLSI设计是微电子领域的皇冠,它涉及将数百万乃至数十亿个晶体管集成到单一芯片上,以实现复杂的功能。

1. 设计层次与抽象

VLSI设计通常在多个抽象层次上进行,这是一种“分而治之”的策略,以管理极端复杂性。

- 系统级:定义芯片的总体功能、性能指标和模块划分。

- 行为级:使用硬件描述语言(如Verilog、VHDL)描述各模块的逻辑功能,不涉及具体电路结构。

- 寄存器传输级(RTL):描述数据在寄存器之间的流动和转换,是逻辑综合的起点,也是设计验证的核心层级。

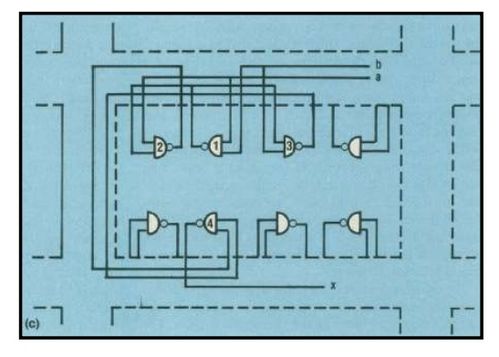

- 逻辑门级:由基本逻辑门(如与门、或门、非门)和触发器构成的网表。

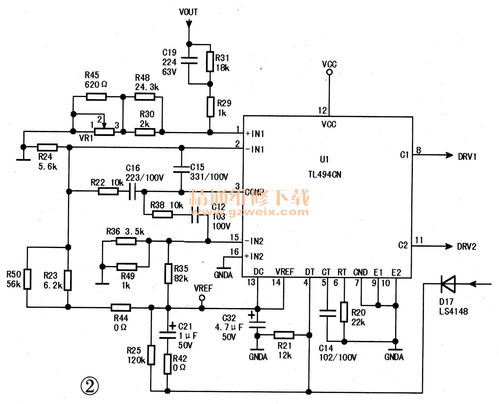

- 电路级:关注晶体管的具体连接方式,构成逻辑门的物理实现,分析时序、功耗等电气特性。

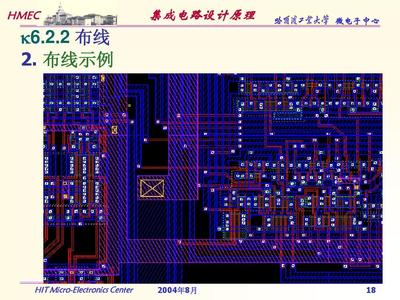

- 版图级:将电路转换为制造所需的几何图形(多边形),定义晶体管、连线的物理形状、尺寸和位置。

设计过程通常是一个自上而下(Top-Down)的设计与自下而上(Bottom-Up)的验证相结合的过程。

2. 设计方法学与流程核心

现代VLSI设计高度依赖于电子设计自动化(EDA)工具和严格的方法学。

- 逻辑综合:将RTL代码自动转换为优化后的门级网表,是连接高层次设计与物理实现的关键桥梁。综合工具会根据设计约束(时序、面积、功耗)和工艺库进行优化。

- 验证:贯穿整个设计流程,确保设计正确性。主要包括:

- 功能验证:通过仿真、形式验证等方法,检查设计行为是否符合规格要求。

- 时序验证:在布局布线后,提取寄生参数,进行静态时序分析(STA),确保在所有工艺角和环境下满足时序要求。

- 物理验证:检查版图是否符合制造规则(DRC)、电路与版图是否一致(LVS)等。

- 可测性设计(DFT):为了提高芯片生产后的测试覆盖率,在设计阶段就插入扫描链、内建自测试(BIST)等结构,使得芯片内部节点能够被控制和观测。

- 低功耗设计:随着工艺进步,功耗密度成为巨大挑战。技术包括时钟门控、电源门控、多电压域、动态电压频率调节(DVFS)等。

3. 物理设计:从网表到芯片

物理设计是将逻辑网表转化为可制造的几何版图的过程,主要包括以下步骤:

- 布图规划:确定芯片核心区域、模块的大致位置和输入输出(I/O)单元排列,规划电源网络。

- 布局:确定标准单元和宏模块在芯片上的精确位置,目标是减少连线长度和时序延迟。

- 时钟树综合(CTS):构建一个低偏斜、低延迟的全局时钟分布网络,确保时钟信号同步到达所有时序单元。

- 布线:根据布局结果,完成单元之间所有逻辑信号的物理连接。分为全局布线和详细布线两步。

- 签核:在交付制造前的最终验证阶段,进行全面的时序、功耗、信号完整性和物理验证。

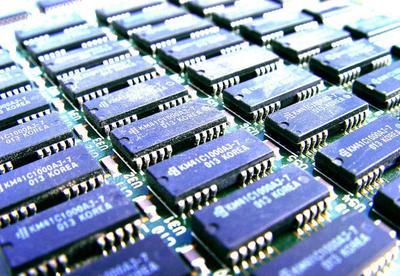

4. 工艺与设计协同优化

VLSI设计与半导体制造工艺紧密耦合。先进的工艺节点(如7nm、5nm)带来了性能提升和面积缩小,但也引入了短沟道效应、寄生效应加剧、制造变异增大等挑战。这要求设计时必须考虑工艺角、器件模型和设计规则,甚至采用新的器件结构(如FinFET)和设计技术协同优化(DTCO)方法。

###

超大规模集成电路设计是一个融合了计算机科学、电子工程、物理学和数学的深度交叉学科。掌握其基本概念是理解现代芯片如何从抽象想法变为手中实体设备的基础。随着人工智能、异构计算等新需求的涌现,VLSI设计方法学仍在不断演进,持续推动着信息技术的边界。